并发知识-硬件内存架构

本文最后更新于:4 个月前

⚡CPU 工作机制

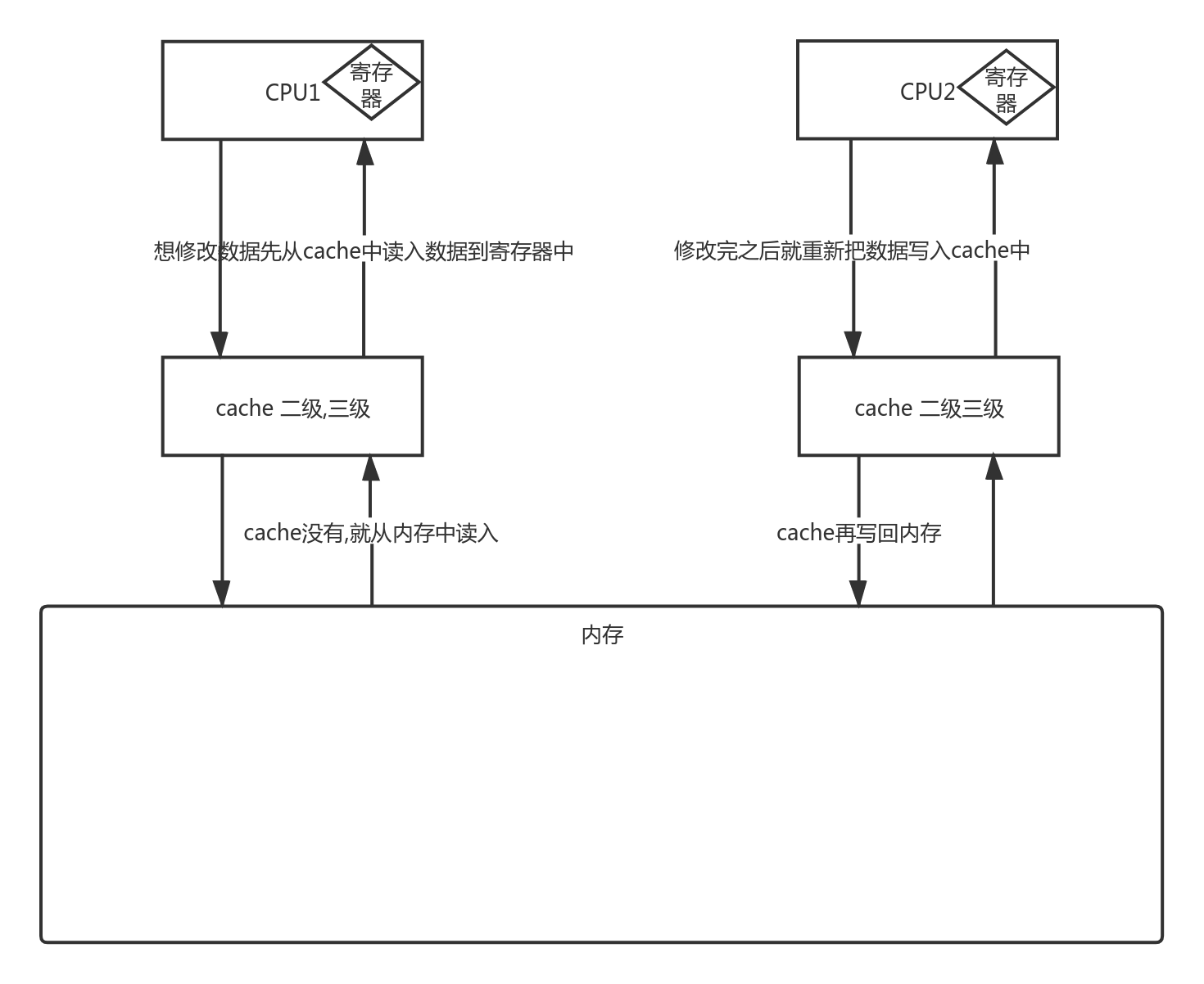

CPU 速度快,但是数据存放到内存中,而内存相对较慢,所以 CPU 中间加上 cache 多级高速缓存来提升数据读取速度

⚡cache 缓存工作机制

-

当 CPU 要去读取一个数据时,会先去缓存中查找,找不到再去内存中找

-

在内存中找到了,同时把这个数据所在的数据快调入缓存中

即把临近的共64 byte 的数据一同载入,因为临近的数据可能被访问的几率更大,下次就可以直接在缓存中查找数据,这样就增加了缓存的命中率(cache hit)了

⚡CPU 缓存一致性问题:

如上图所示,cache 之和特定的 CPU 进行通信,多核 CPU 就会出现并发问题: 一个线程在读,另一个在写,导致数据不一致问题

- 解决方案:

-

总线锁

使用 CPU 提供的一个 LOCK# 信号,当一个处理器在总线上输入此信号,其他处理器的请求将被阻塞,那么该处理器就可以独占共享锁

todo为什么是共享锁?粒度比较大,会降低 CPU 的吞吐量 [1]

-

缓存锁(缓存一致加锁)

控制锁的粒度,核心是缓存一致协议,不同的 CPU 厂商有不同的实现方式,例如 MESI: 当修改变量时,如果数据是共享变量,会将 cache line 置为无效,所以其他的 CPU 就从内存中读数据,不会再去 cache 中读取数据

-

⚡线程和硬件架构

进程 -> 线程 -> os 内核线程 -> CPU 线程

本博客所有文章除特别声明外,均采用 知识共享署名-非商业性使用-相同方式共享 4.0 国际许可协议 。转载请注明出处!